Meet Our Team

M Sadman Sakib

Role: Memory controller, VPU, Integration, I/O

I began by setting up the memory controller and configuring the memory mappings for the entire system. While BRAM served as our primary memory, we also integrated the FPGA's SDRAM to expand the available memory resources. Additionally, I contributed to the development and testing of our 4-lane, 32-bit Vector Processing Unit (VPU). In the later stages of the project, I assisted in enabling the audio I/O functionality and played a key role in integrating the various subsystems into a cohesive and functional design.

LinkedIn Profile

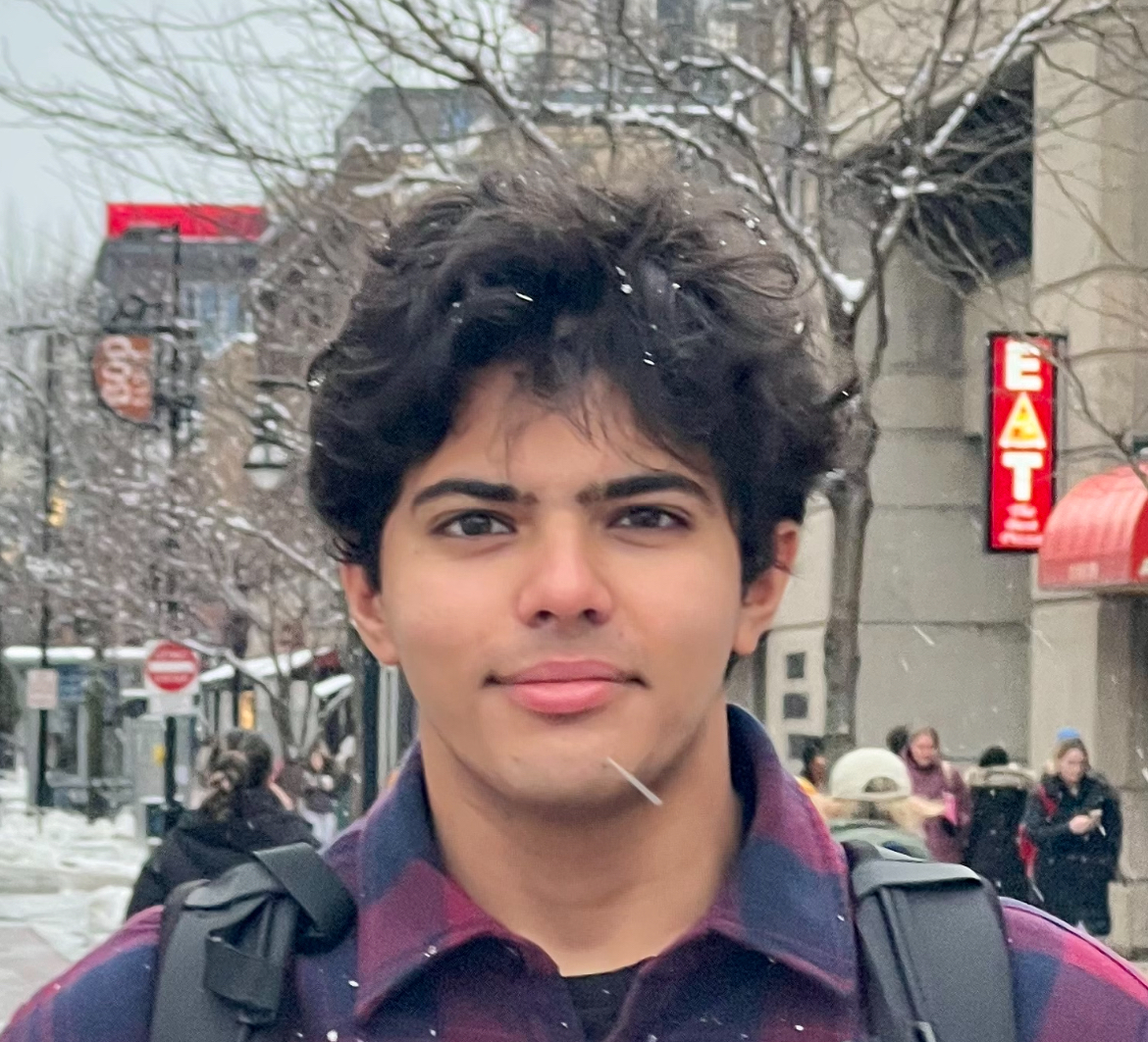

Rohan Rao

Role: VPU, Code, Graphics

I worked on the VPU Design (Vector Processing Unit), Code and Graphics. I also worked on the code integration ensuring everything runs smoothly on our co-processor. Lastly, I worked on graphics including MIF File creation, Drawing and Masking Logic as well as ROM initalization for images used in our game.

LinkedIn Profile

Aditi Shah

Role: CPU, Audio

I contributed to building and testing of the RISC-V CPU, starting with Ibex and later transitioning to PicoRV32. I worked with the audio input subsystem, and assisted in developing initial VGA graphics. Additionally, I supported system integration to bring the full product together on hardware.

LinkedIn Profile

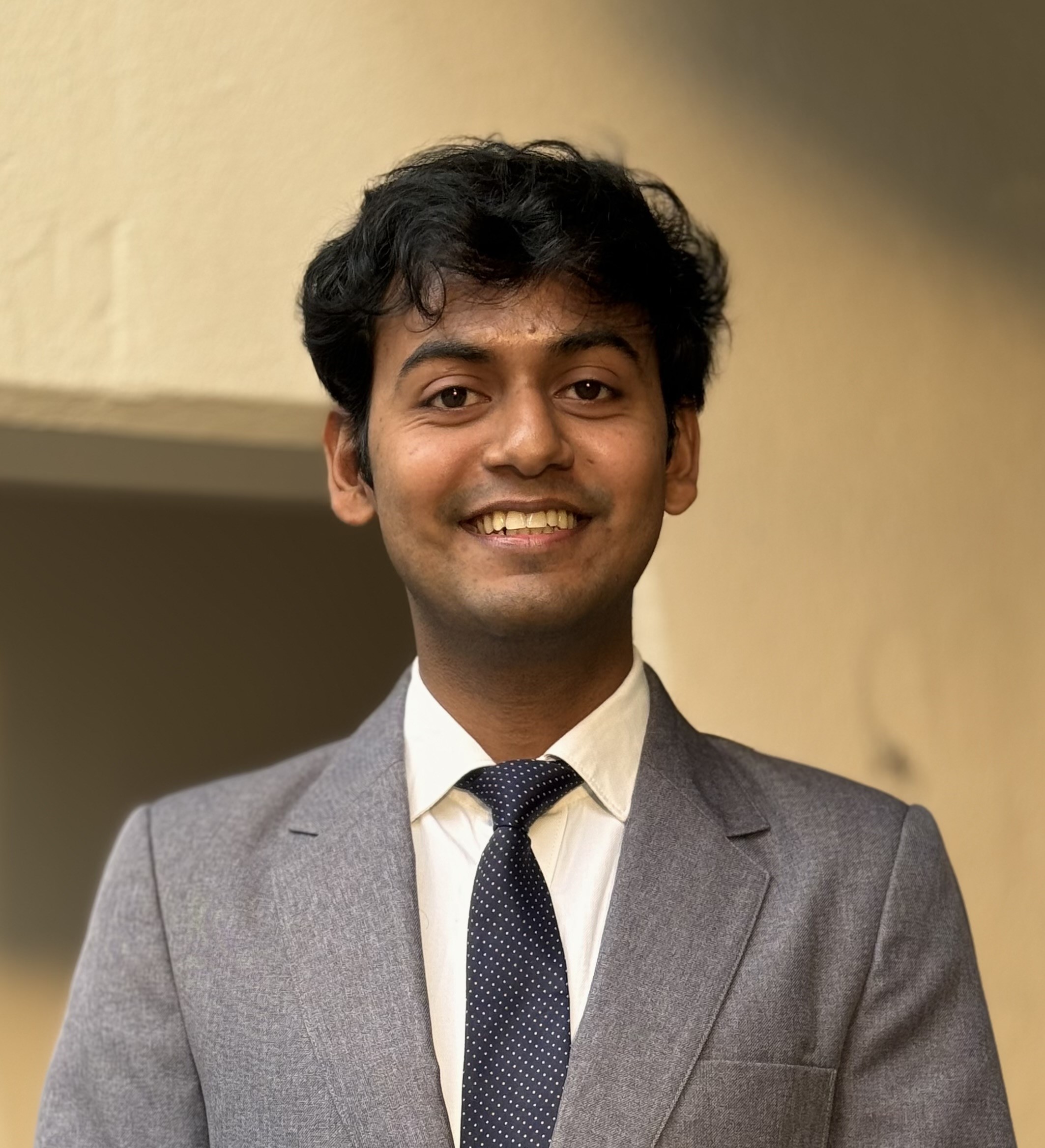

Asish Das

Role: Software, IO, assist in Hardware design (audio codec)

I primarily focused on the software side, including configuring the toolchain, help develop the programming logic, and debugging. I also supported other team members with hardware testing and refining the game control flow. Additionally, I worked on converting a speech-to-text model into a C file for deployment on the FPGA. While we're currently facing quantization issues, we will address this in the future.

LinkedIn Profile